МІНІСТЕРСТВО ОСВІТИ І НАУКИ УКРАЇНИ

ХАРКІВСЬКИЙ НАЦІОНАЛЬНИЙ УНІВЕРСИТЕТ РАДІОЕЛЕКТРОНІКИ

Кафедра МТС

ЗВІТ

з дисципліни «Проектування пристроїв на мікроконтролерах і ПЛІС. ПЛІС»

з теми «Знайомство з VIVADO»

| Виконав: студент групи АКТАКІТ-18-2 Ковальов М.В. | Перевірив: викладач кафедри МТС Сайківська Л.Ф. |

2021

Знайомство з VIVADO

1 Мета роботи

Знайомство з процесом проектування з використанням програмного забезпечення Xilinx Vivado для створення простої цифрової схеми з використанням VHDL.

2 Опис лабораторної роботи та завдання для виконання

Завдання: створити проект Vivado, провести необхідні аналізи в програмному забеспеченні Vivado та заванатажити программу на ПЛІС Nexys4.

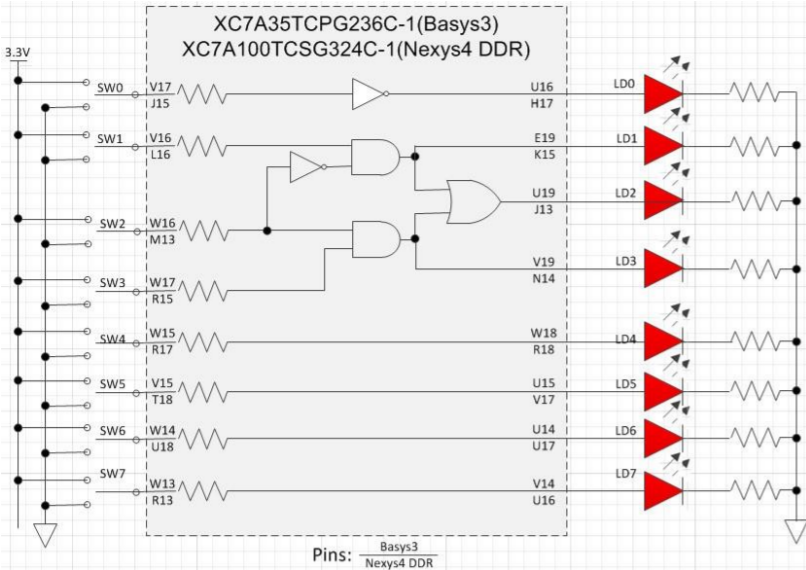

Схема проекту наведена на рис 1. Проект складається з кількох входів, підключених до светоизлучающим діодів та зсувними перемикачів. Деякі входи підключені до діодів безпосередньо, деякі з допомогою логічних елементів.

малюнок

Рисунок 1 – Схема електрична принципова для моделювання

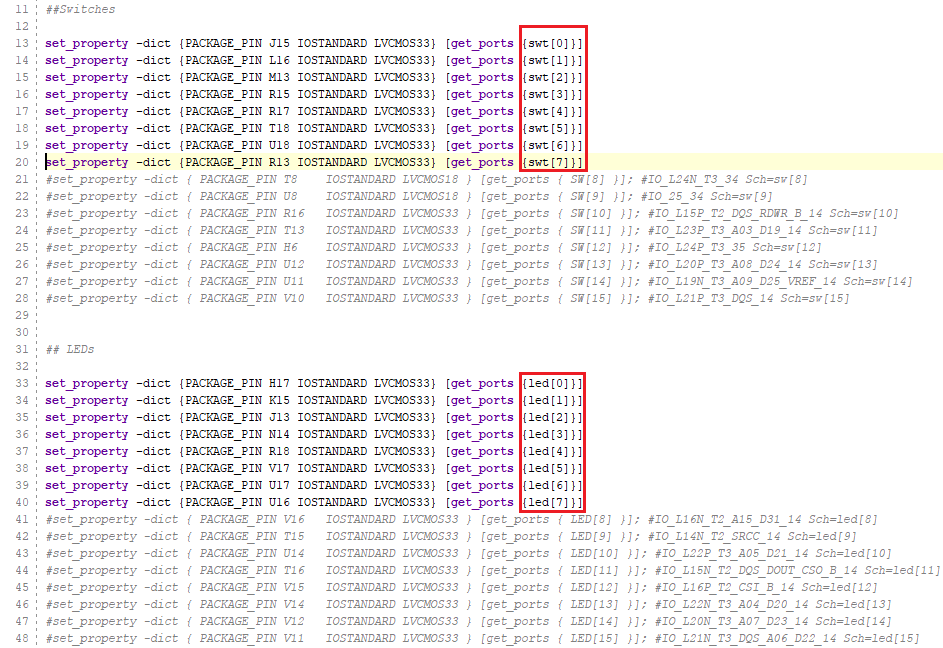

Після запуску програмного забезпечення Vivado було створено новий проект в який було завантажено файл tutorial.vhd. Після створення проекту, відкрили файл tutorial.vhd в текстовому вигляді та проаналізували його вміст, після відкрили джерело Nexys4DDR_Master.xdc та проаналізували вміст.

Відкривши вкладку обмежень розкоментували SW[7:0] та LED[7:0] прибравши знак #.

Рисунок 2 – Редагування файла DDR Master XDC

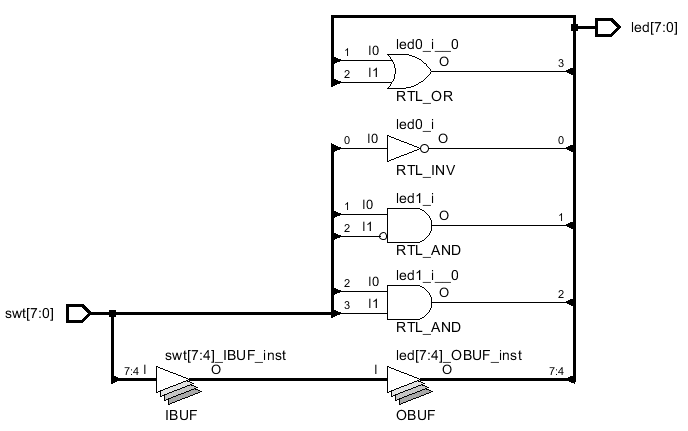

Виконали аналіз RTL отримали наступну схему яка описує логічний вигляд проекту рис 3.

Рисунок 3 – Логічний вигляд проекту

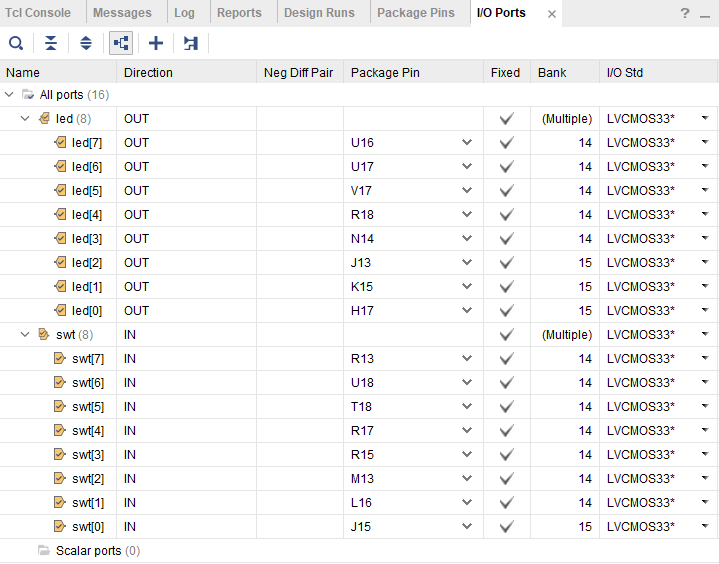

Після перемикання рівнів з базового на I/O Planning layout отримали картину розміщення виводів та їх конфігурацію рис 4.

Рисунок 4 – Порти введення та виведення та їх призначення

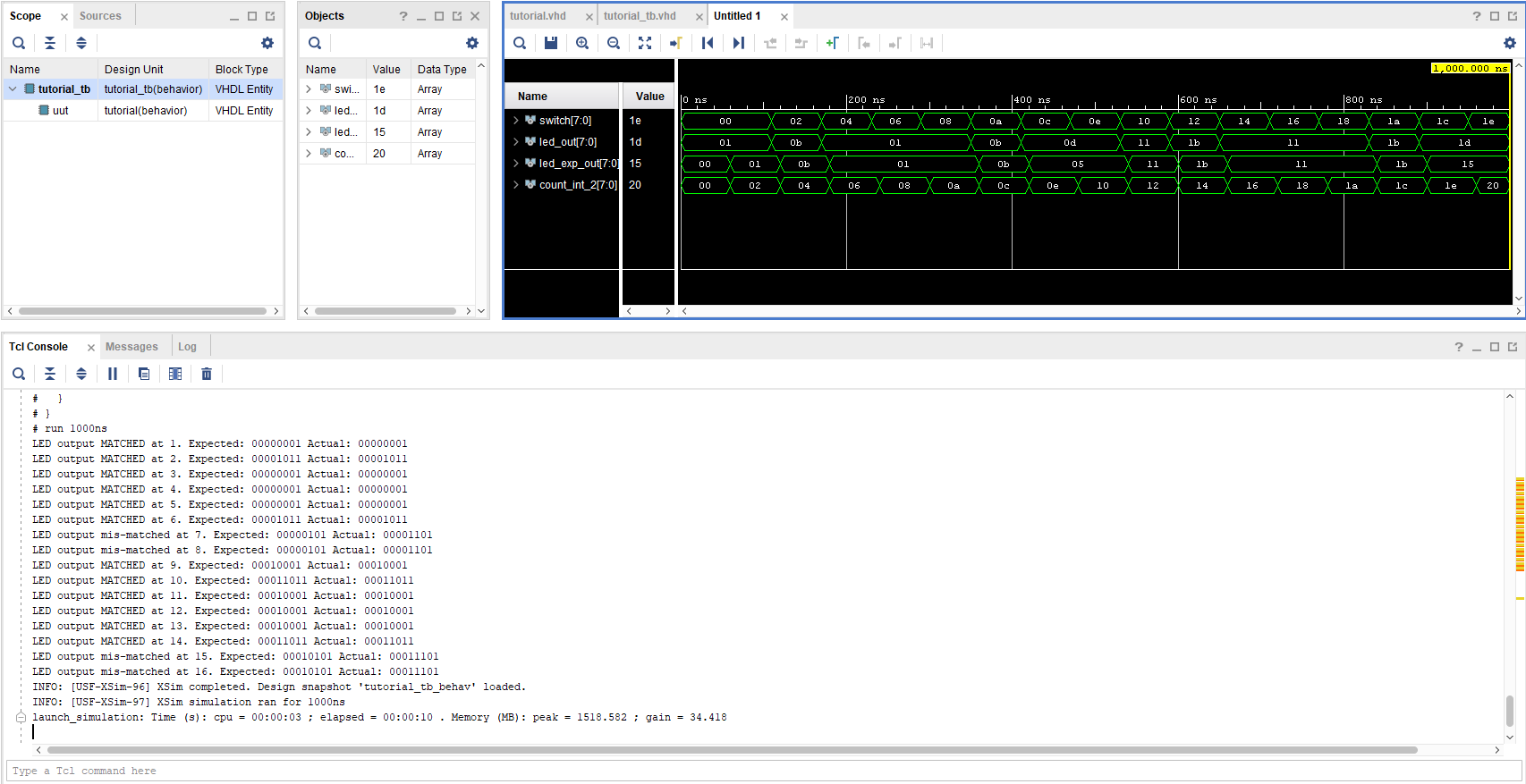

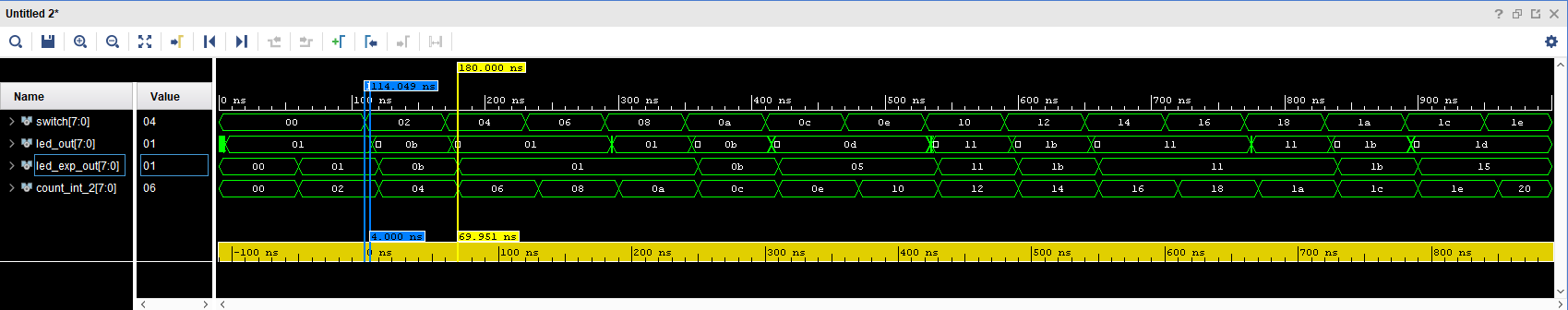

Після цього провели симуляцію на періоді в 1000 нс та отримали наступний вигляд сигналів (рис5).

Рисунок 5 – результат симуляції на 1000нс

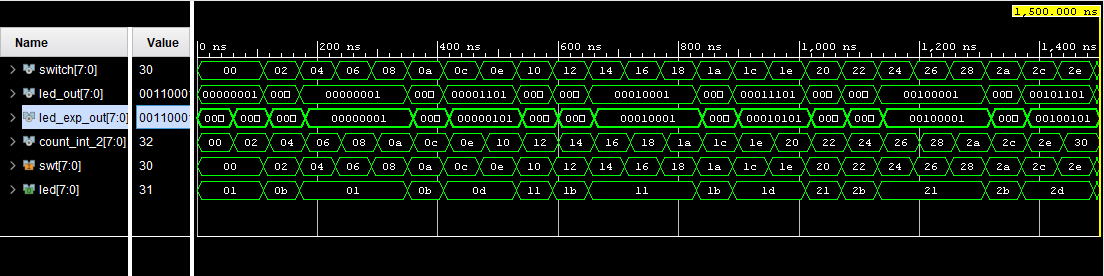

Після першої симуляції продовжили час симуляції ще 500 нс та провели симуляцію (рис 6).

Рисунок 6 – результат симуляції на 1500нс

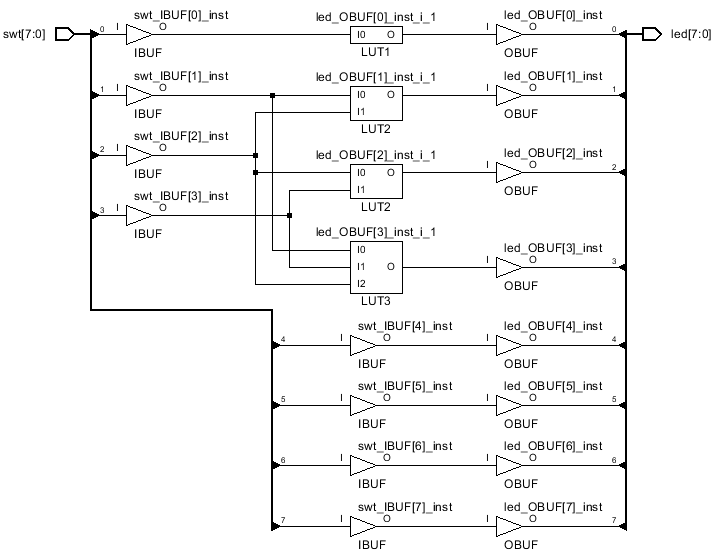

Після симуляції проекту було проведено синтез проекту в результаті чого було отриману схему підключення swt та led (рис 7).

Рисунок 7 – Схема підключень swt та led

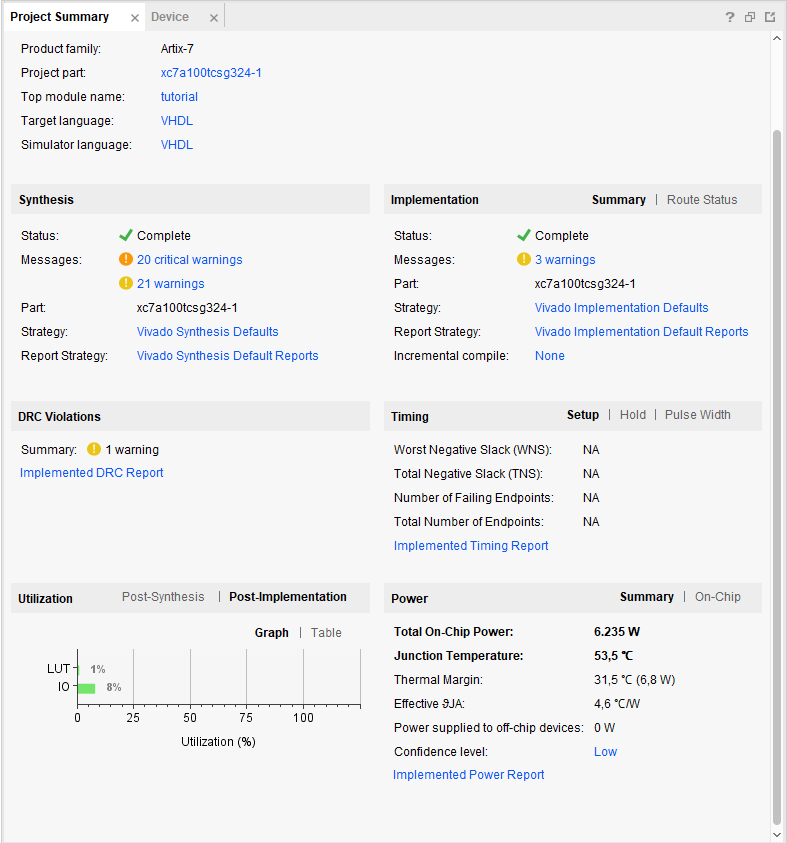

Після проведення синтезу було проведено імплементацію (рис 8), часове моделювання (рис 9).

Рисунок 8 – Project Summary після виконання імплементації

Рисунок 9 – Результат часового моделювання

ВИСНОВКИ

На лабораторній роботі ознайомилися з процесом проектування та використанням програмного забезпечення Xilinx Vivado для створення простої цифрової схеми з використанням VHDL. Було створено новий проект в який завантажили вже готові файли, які були видано викладачем, для RTL аналіз, крім того отримали схему логіки проекту та можливість перейти на вкладку для налаштування відповідності віртуальних портів та реальних. Буди проведені симуляцію та отримали набір сигналів який відповідає генерації бітів даних, синтез проекту за допомогою якого отримали схему підключення перемикачів та діодів та імплементацію.