Суматори. Принцип роботи. Схеми суматорів.

Найпростішим елементом, що підсумовує, є напівсуматор. Він має два входи А і В і два виходи: S (cума) і P (перенесення) (рис. 6.1,а).

а) б)

Рис. 6.1. Умовне графічне позначення напівсуматора (а), повного однорозрядного суматора (б)

Позначенням напівсуматора служать букви НS (Нalf Sum). Його робота описується рівняннями

Процедуру складання двох n-розрядних двійкових чисел можна представити таким чином. Складання цифр А0 і В0 молодшого розряду дає біт суми S0 і біт перенесення P1. У наступному розряді здійснюється складання цифр А1, В1, та Р1, що формують біт суми S1 і перенесення Р2.

Повний однорозрядний суматор має три входи (рис.6.1,б): два для доданків А і В і один для сигналу перенесення з попереднього розряду.

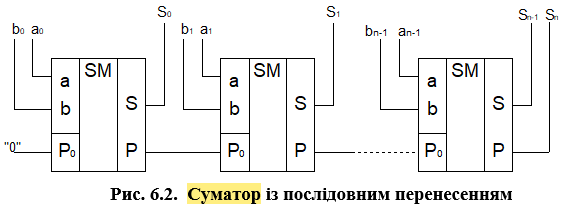

На рис. 6.2 принцип дії n-розрядного суматора з послідовним перенесенням.

Число суматорів = числу розрядів. Вихід перенесення Р кожного суматора з’єднаний із входом перенесення наступного, більш старшого розряду. На вході перенесення суматора молодших розрядів встановлений «0», оскільки сигнал перенесення сюди не надходить. Доданки Аi і Bi складаються в усіх розрядах одночасно, а перенесення Р надходить із закінченням операції складання в попередньому розряді.

Час перенесення можна зменшити, якщо ввести паралельне перенесення, для чого застосовують спеціальні вузли-блоки прискореного перенесення. Вони мають складну схему і збільшенням числа розрядів складність настільки зростає, що їхнє виготовлення стає недоцільним. У вигляді окремих мікросхем випускаються однорозрядні, дворозрядні і чотирирозрядні суматори. У сімействі ТТЛ це мікросхеми відповідно К155ИМ1 (аналоги SN7480N, SN7480J), ИМ2 та ИМ3.

Паралельні регістри. Схеми, принцип роботи.

Паралельні регістри – це пристрої, призначені для запису, зберігання та видачі інформації, представленій у вигляді двійкових кодів. Для зберігання кожного двійкового розряду в регістрі використовується однa комірка тригера. Для запам’ятовування багаторозрядних слів необхідне число тригерів об’єднують разом і розглядають як єдиний функціональний вузол-регістр. Типовими зовнішніми зв’язками регістра є інформаційні входи D, вхід сигналу запису З, вхід гасіння R, виходи тригерів Q. У спрощеному варіанті регістр може не мати входу гасіння та інверсних виходів.

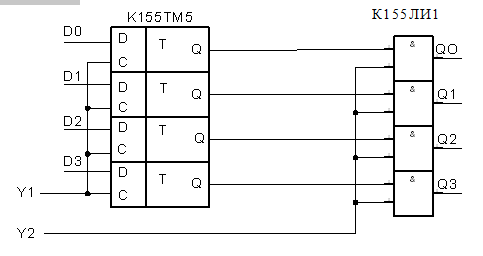

На рис. 7.1 показана схема чотирирозрядного регістра, виконаного на ІМС К155ТМ5 і К155ЛИ1. При подачі сигналу управління Y1 = 1 інформація по входах Х1–Х4 записується одночасно у відповідні розряди чотирьох D-тригерів. При Y1 = Y2 = 0 інформація зберігається в регістрі пам’яті, а при Y2 = 1 відбувається паралельне зчитування інформації.

Рис.7.1. Чотирирозрядний паралельний регістр

Умовне зображенням регістра показане на рис. 7.2.

Рис. 7.2. Умовне зображення регістра

Регістри, що випускаються промисловістю, інодіоб’єднують на кристалі мікросхеми з іншими вузлами, у парі з якими регістри часто використовуються у схемах цифрової апаратури. Приклад такого комплексного вузла – мікросхема багаторежимного буферного регістра (МБР) К589ИР12, основу якої становить восьмирозрядний регістр із входами DO – D7, C, R і вісьмома виходами Q0 – Q7, забезпеченими підсилювачами потужності (буферами) із трьома станами виходу. Крім того, до складу мікросхеми входять декілька елементів управління. Підсилювачі із трьома станами виходу має і чотирирозрядний регістр К155ИР15, побудований на тригерах, що керуються суворо фронтом.

Різновиди оперативної пам'яті. Побудова блоків ОЗП

Оперативна пам’ять (Random Access Memory – RAM) пам’ять з довільним доступом, використовується центральним процесором для сумісного зберігання даних і виконуваного програмного коду. За принципами зберігання інформації ОЗП можна розподілити на статичні та динамічні. Оперативну пам’ять можна розглядати як певний набір комірок, кожна з яких може зберігати один інформаційний біт.

У статичних ОЗП комірки побудовані за різними варіантами тригерів. Після запису біта в таку комірку вона може зберігати його скільки завгодно довго – необхідна тільки наявність живлення. Звідси й назва пам’яті – статична, тобто така, що перебуває в незмінному стані. Показник статичної пам’яті є її швидкодія, а недоліками – високе енергоспоживання й низька питома щільність даних, оскільки одна комірка тригера складається з декількох транзисторів і, отже, займає на кристалі чимало місця.

У динамічних ОЗП елементарна комірка являє собою конденсатор, виконаний за КМОН-технологією. Він здатний протягом декількох мілісекунд зберігати електричний заряд, наявність якого можна асоціювати з інформаційним бітом. При записі логічної одиниці в елемент пам’яті конденсатор заряджається, при записі нуля – розряджається. При зчитуванні даних конденсатор розряджається, і якщо його заряд був ненульовим, то на виході схеми зчитування встановлюється одиничне значення. Процес зчитування (звернення до комірки) поєднується з відновленням (регенерацією) заряду. Якщо звернення до комірки не відбувається протягом довгого часу, то конденсатор за рахунок струмів витоку розряджається і інформація втрачається. Для компенсації витоку заряду періодично циклічно звертаються до елементів пам’яті, тому що кожне звертання відновлює попередній заряд конденсатора. До переваг динамічної пам’яті належать висока щільність розміщення даних і низьке енергоспоживання, а до недоліків – низька швидкодія порівняно зі статичною пам’яттю. У даний час динамічна пам’ять (Dynamic RAM – DRAM) використовується як оперативна пам’ять комп’ютера, а статична пам’ять (Static RAM – SRAM) – для створення високошвидкісної кеш-пам’яті процесора.

1 2 3 4 5 6 7 8 9